RELATED POSTS:

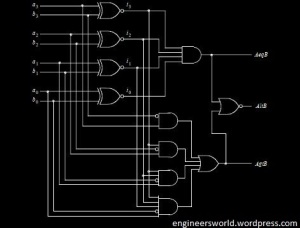

1.VHDL Code for 4 bit comparator

3.VHDL code for 2 to 4 binary decoder

______________________________________________________________________________

Here is the VHDL code for FULL ADDER:

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY fulladd IS

PORT ( Cin, x, y : IN STD_LOGIC ;

s, Cout : OUT STD_LOGIC ) ;

END fulladd ;

ARCHITECTURE beh OF fulladd IS

BEGIN

s <= x XOR y XOR Cin ;

Cout <= (x AND y) OR (Cin AND x) OR (Cin AND y) ;

END beh ;

Subscribe us for more such details directly to your mail,and write here for any of your queries and suggestions.